华为鲲鹏920处理器 916处理器

| 鲲鹏920系列 | |||||||

| 型号 | 7265 | 7260 | 5255 | 5250 | 5230 | 5220 | 3210 |

| 核心 | 64 | 64 | 48 | 48 | 32 | 32 | 24 |

| 主频 | 3 | 2.6 | 3 | 2.6 | 2.6 | 2.6 | 2.6 |

| 内存通道 | 8 | 8 | 8 | 8 | 8 | 4 | 4 |

| TPD功耗 | 200 | 180 | 170 | 150 | 120 | 115 | 95 |

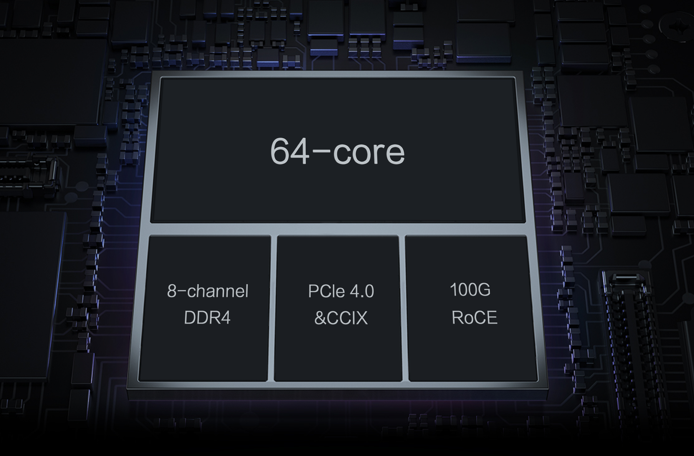

多核架构

2个CPU Die,每个CPU Die包括最多32个核、4个DDR4内存控制器

1个IO Die,提供:PCIe接口、以太网络接口、存储控制器、片间缓存一致接口和硬件加速引擎等功能

多合一SOC

CPU | 南桥 | 网卡 | 硬盘控制器 等多个芯片功能合一支持多种数据加解密、压缩/解压缩机制

极致性能

单处理器整型计算性能,相比上一代提升2.9倍

加速大数据、分布式存储和数据库等场景的并行计算性能

海量吞吐

支持8个DDR4内存通道,内存带宽提升60%

支持PCle 4.0, IO带宽提升66%

支持100GE以太网络,网络带宽提升4倍

片间互联

华为Cache一致性总线(HCCS),为内核、设备、集群提供系统内存的一致访问

片间带宽最高可达480Gbps,实现最多4个鲲鹏920处理器互联和最高256个物理核的NUMA架构

| 组件 | 规格 |

|---|---|

| 计算核 | 兼容Arm v8.2架构,华为自研核主频最高3.0GHz,单处理器最高可集成64核 |

| 缓存 | L1: 64 KB instruction cache and 64 KB data cache L2: 512 KB private per core L3: 24–64 MB shared for all(1 MB / core) |

| 内存 | 8 DDR4 channels per socket, up to 3200 MHz |

| 互联 | 华为HCCS互联协议,支持最高4路互联 |

| I/O | 40 PCIe Gen 4.0 lanes 2 x 100GE, RoCEv2/RoCEv1, CCIX x4 USB 3.0, x16 SAS 3.0, x2 SATA 3.0 |

| 封装 | 60 mm x 75 mm, BGA |

| 功耗 | TDP:100-200 W |

鲲鹏916是一颗32核心处理器

指令集简介

更新时间:2020/03/14 GMT+08:00查看PDF分享

华为鲲鹏处理器基于Arm架构。Arm是一种CPU架构,有别于INTEL、AMD CPU采用的CISC复杂指令集,Arm CPU采用RISC精简指令集(reduced instruction set computer,精简指令集计算机)。

传统的CISC体系由于指令集庞大,指令长度不固定,指令执行周期有长有短,使指令译码和流水线的实现在硬件上非常复杂,给芯片的设计开发和成本的降低带来了极大困难。

随着计算机技术的发展需要不断引入新的复杂的指令集,为支持这些新增的指令,计算机的体系结构会越来越复杂。然而,在CISC指令集的各种指令中,其使用频率却相差悬殊,大约有20%的指令会被反复使用,占整个程序代码的80%。而余下的80%的指令却不经常使用,在程序设计中只占20%,显然,这种结构是不太合理的。

针对这些明显的弱点,1979年美国加州大学伯克利分校提出了RISC(Reduced Instruction Set Computer,精简指令集计算机)的概念。RISC并非只是简单地去减少指令,而是把着眼点放在了如何使计算机的结构更加简单合理地提高运算速度上。

RISC结构优先选取使用频率最高的简单指令,避免复杂指令。将指令长度固定,指令格式和寻址方式种类减少。以控制逻辑为主,不用或少用微码控制等措施来达到上述目的。

Arm架构具有更好的并发性能,匹配业务特征能耗比更佳,更加灵活丰富的选择,业界热点快速发展。

华为鲲鹏处理器兼容Armv8指令集,详细信息请参考《Arm® Architecture Reference Manual Armv8, for Armv8-A architecture profile》。

本文档详细描述了华为鲲鹏920处理器指令替换的相关案例,主要适用于使用华为鲲鹏920处理器的以下人员:

软件开发人员

应用移植人员